Edif Netlist File Format

ISE Design Suite: Embedded Edition

The ISE Design Suite: Embedded Edition includes Xilinx Platform Studio (XPS), Software Development Kit (SDK), large repository of plug and play IP including MicroBlaze™ Soft Processor and peripherals, and a complete RTL to bit stream design flow. Embedded Edition provides the fundamental tools, technologies and familiar design flow to achieve optimal design results. These include intelligent clock gating for dynamic power reduction, team design for multi-site design teams, design preservation for timing repeatability, and a partial reconfiguration option for greater system flexibility, size, power, and cost reduction.

ISE Design Suite: System Edition

The ISE Design Suite: System Edition builds on top of the Embedded Edition by adding on System Generator for DSP™. System Generator for DSP is the industry's leading high-level tool for designing high-performance DSP systems using Xilinx programmale devices, providing system modeling and automatic code generation from Simulink® and MATLAB® (The MathWorks, Inc.)

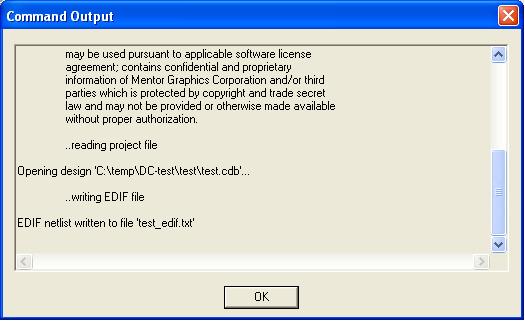

The netlist is written in a single file, but includes four sections: 1) A file header, 2) A table listing each of the components, 3) A table listing each of the net names, 4) A table listing each of the net connections. Yosys is controlled using synthesis scripts. For example, the following Yosys synthesis script reads a design (with the top module mytop) from the verilog file mydesign.v, synthesizes it to a gate-level netlist using the cell library in the Liberty file mycells.lib and writes the synthesized results as Verilog netlist to synth.v.

ISE Design Suite: WebPACK Edition

ISE WebPACK delivers a complete, front-to-back design flow providing instant access to the ISE features and functionality at no cost. To learn more, please visit ISE WebPACK Design Software landing page.

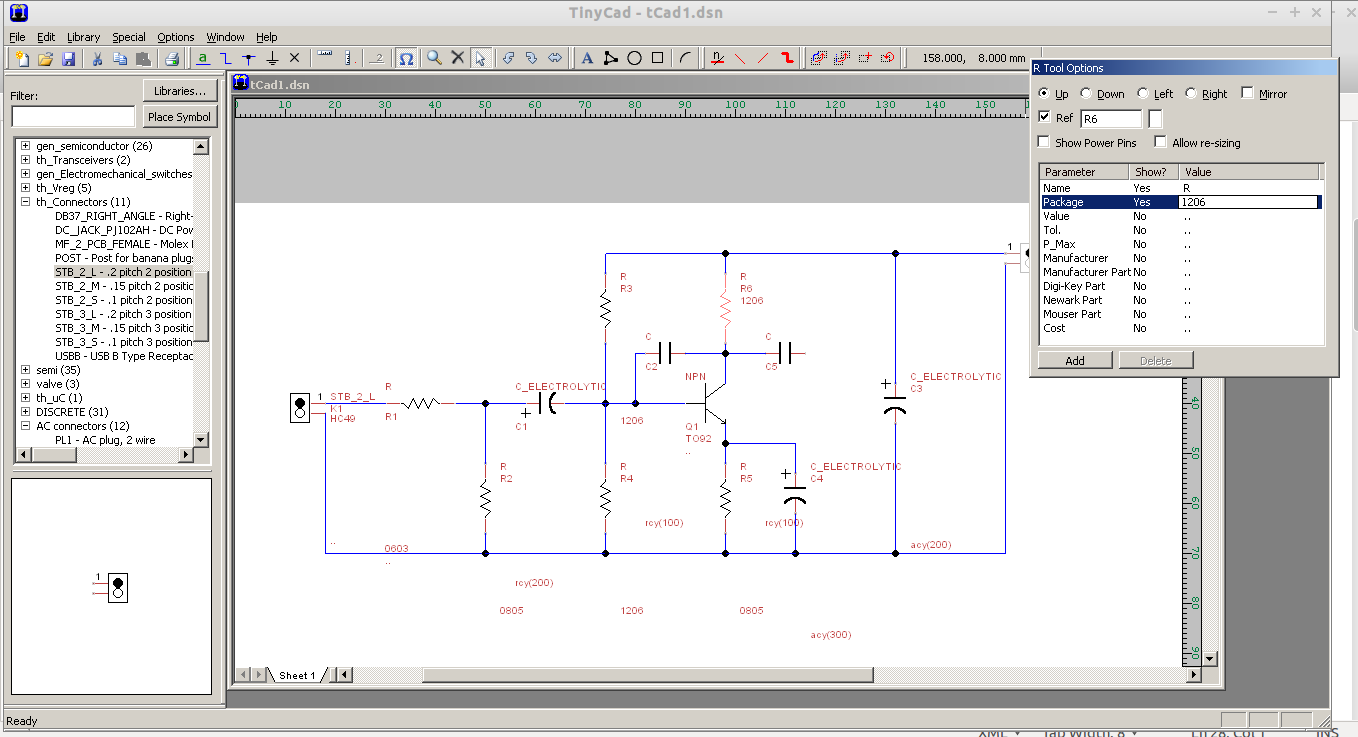

Pcb Netlist

Additional Options

The ISE Design Suite also offers a-la-carte tools to enhance designer productivity and to provide flexible configurations of the Design Suite Editions.

Netlist Format

- High-Level Synthesis – Vivado High-Level Synthesis accelerates IP creation by enabling C, C++ and System C specifications to be directly targeted into Xilinx programmable devices without the need to manually create RTL.

- Partial Reconfiguration – Xilinx Partial Reconfiguration technology allows designers to change functionality on the fly, eliminating the need to fully reconfigure and re-establish links, dramatically enhancing the flexibility that FPGAs offer.

- ChipScope – The ChipScope Pro Serial I/O Toolkit provides a fast, easy, and interactive setup and debug of serial I/O channels in high-speed FPGA designs for use with the WebPACK edition.

- Embedded Development Kit – The Embedded Development Kit (EDK) is an integrated development environment for designing embedded processing systems for use with WebPACK edition.

- System Generator for DSP – The industry’s leading high-level tool for designing high-performance DSP systems using Xilinx devices for use with the WebPACK edition.